## RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE UNIVERSITÉ IBN KHALDOUN DE TIARET.

#### FACULTÉ DES SCIENCES APPLIQUÉES DÉPARTEMENT de GÉNIE ÉLECTRIQUE

#### Mémoire de fin d'études en vue de l'obtention du diplôme de Master

Spécialité : Génie Electrique

Option: Informatique Industrielle

Présenté par :

AMEUR MANSOUR KARIMA AMAR SOUAD

#### Sujet du mémoire

Contribution à la Conception d'un AOP basse tension en technologie CMOS 90nm pour des circuits biomédicaux.

Soutenu publiquement devant le jury composé de :

Mr, ALLAOUI Président

Mr, ACED.M.R Examinateur

Mr, F.MOULAHCENE Encadreur

Mr, Y.BELHADJI Co-Encadreur

**PROMOTION: 2015**

### Dédicace

Je dédie ce modeste travail :

À ma belle-mère;

À la mémoire de mon père ;

À mes proches mes sœurs Keltoum, Fatima, Nawel

et mon frère Abdelkader.

À mon amie Ameur Mansour Karima;

À toute la famille AMAR et CHAHROUR;

À A touts mes chers amis, à FATIHA, ALIA et AMEL;

Sans oublierMs: Bouzidi

À tous mes chers enseignants qui ont enseigné moi;

Amar Souad

#### A mon père

Pour sa patience et ces considérables sacrifices pour me parvenir à ce niveau.

#### A ma mère

Pour son grand amour, ces sacrifices et toute affectation qu'elle m'a toujours offerte.

À mes proches mes sœurs Bakhta, Dhoha, Amaria et mes frère Abdelkader et sa femme, Mohamed.

À mon amie Amar Souad;

À toute la famille Ameur Mansour;

À touts mes chers amis, ALIA et AMEL; Sans oublierms : Bouzidi À tous mes chers enseignants qui ont enseigné moi ;

Ameur Mansour Karima

### Remerciement

Avant tout nous tenons a remercier notre Dieu de nos avoir donné la force et le courage.

A la suite Nous tenons à remercier vivement M.F.MOULAHCENE et Mr.Y.BELHADJI

Notre promoteur qui a fourni des efforts énormes, par ses informations ses conseils et ses encouragements.

Nous tenons également à remercier monsieur les membres de jury pour l'honneur qu'ils nos ont fait en acceptant de siéger à notre soutenance, tout particulièrement : Mr. Aced .M.R pour nous avoir fait l'honneur de présider le jury de cette mémoire.

Nos vifs remerciements aussi à Mr. Tiffour.A , pour avoir accepté d'être examinateurs de ce travail.

Et tous les enseignants de département de Génie électrique et Informatique Industriel

Nos plus chaleureux remerciements pour tous ceux qui de prés et de loin ont contribué à la réalisation de ce mémoire.

### Liste de figure

| Figure      | Titre                                                                                                                                                | Page |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

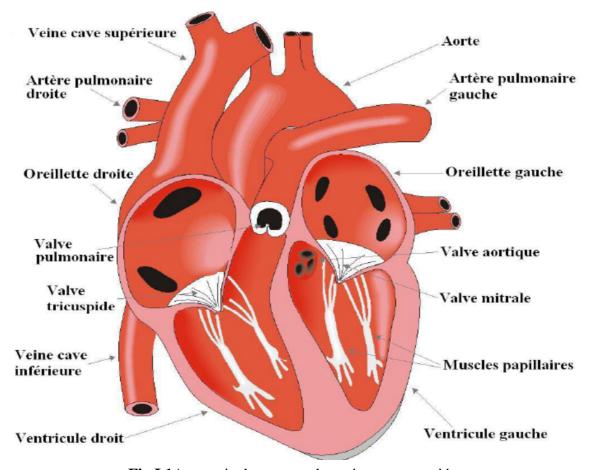

| Fig. I.1    | Anatomie du cœur et des vaisseaux associés.                                                                                                          | 5    |

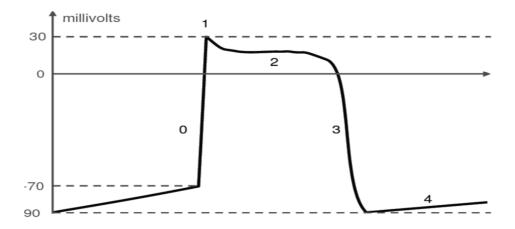

| Fig. I.2    | Les cinq phases du potentiel d'action d'une cellule du muscle.                                                                                       | 7    |

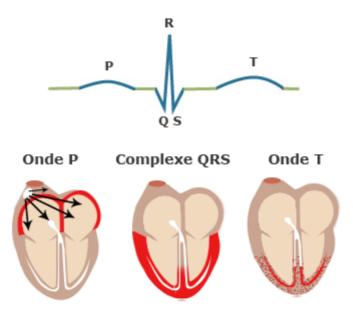

| Fig.I.3     | Étapes successives de dépolarisation/repolarisation du cœur qui se traduisent sur le plan électrocardiographique par différentes ondes P, QRS, et T. | 8    |

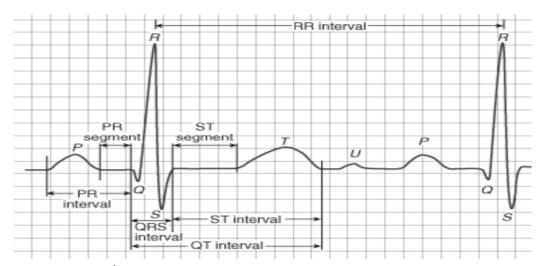

| Fig.I.4     | Étapes successives de dépolarisation/repolarisation du cœur qui se traduisent sur le plan électrocardiographique par différentes ondes P, QRS, et T. | 9    |

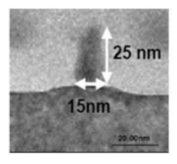

| Fig. II.1.  | Évolution de la technologie : de la lampe triode (a) au MOSFET.                                                                                      | 10   |

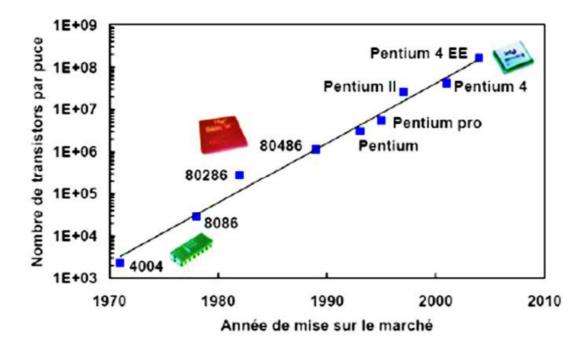

| Fig. II. 2. | Illustration de la loi de Moore : évolution du nombre de transistors dans les microprocesseurs Intel                                                 | 11   |

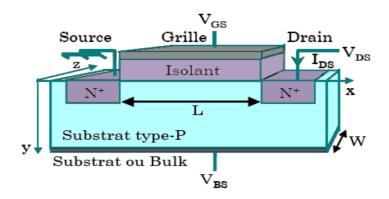

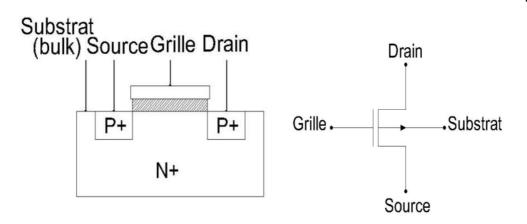

| Fig. II.3.  | Vue schématique du transistor MOS de type N                                                                                                          | 11   |

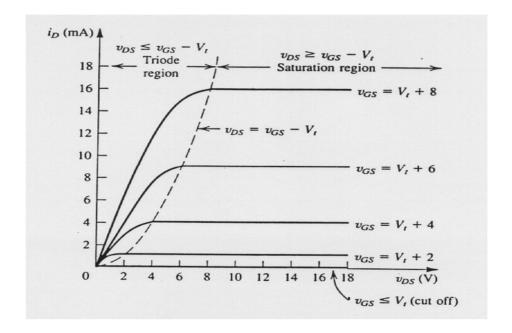

| Fig. II.4.  | Caractéristiques d'un transistor MOSFET à canal N.                                                                                                   | 13   |

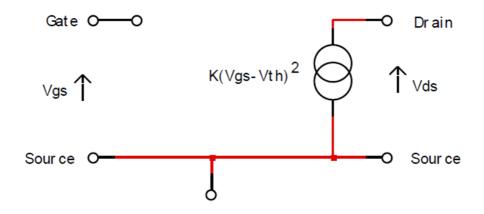

| Fig. II.5.  | Schéma équivalent grands signaux d'un MOSFET                                                                                                         | 14   |

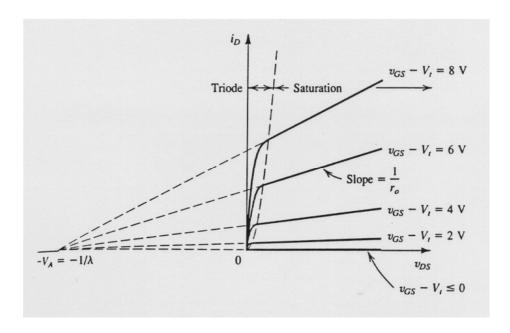

| Fig. II.6.  | Résistance de sortie du MOSFET.                                                                                                                      | 15   |

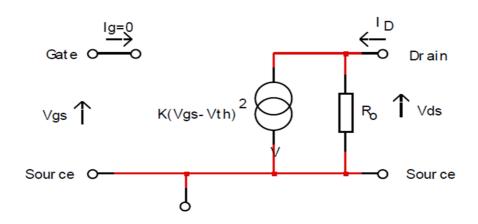

| Fig. II.7.  | schéma équivalent grands signaux du MOSFET                                                                                                           | 16   |

| Fig. II.8   | Transistor MOS à canal N                                                                                                                             | 18   |

| Fig. II.9.  | Transistor MOS à canal P                                                                                                                             | 18   |

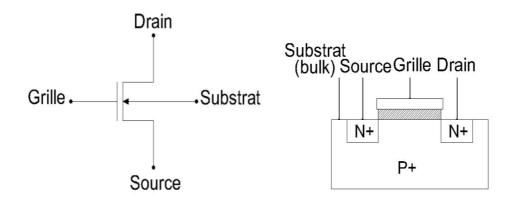

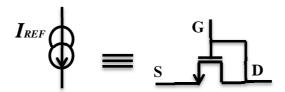

| Fig.II.10   | Le schéma de principe d'un miroir de courant                                                                                                         | 20   |

| Fig.II.11   | Miroir de courant simple à 2 MOS                                                                                                                     | 20   |

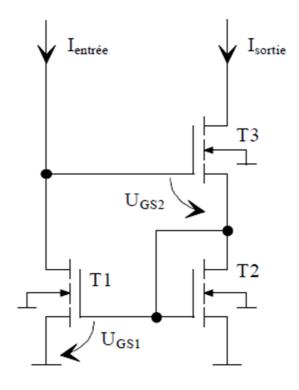

| Fig.II.12   | Miroir de courant WILSON                                                                                                                             | 22   |

| Fig.II.13   | Miroir de courant cascode                                                                                                                            | 23   |

| Fig. II.14  | Schéma d'un Amplificateur opérationnel idéal                                                                                                         | 25   |

| Fig.II.15   | Caractéristique de transfert – Offset                                                                                                                | 27   |

| Fig. II.16  | Schéma d'un Amplificateur opérationnel réel                                                                                                          | 27   |

| Fig. II.17  | Amplificateur non inverseur                                                                                                                          | 28   |

| Fig.II.18   | Architecture interne d'un AOP CMOS                                                                                                                   | 29   |

| Fig. II.20. | Schéma principale de la technique CHS.                                                                 | 32 |

|-------------|--------------------------------------------------------------------------------------------------------|----|

| Fig.II.21   | Transformée de Fourier du signal de sortie idéal sans bruit                                            | 33 |

| Fig. III.2  | .Résultats de la simulation                                                                            | 36 |

| Fig. III.3  | Résultats de la simulation                                                                             | 37 |

| Fig. III.4. | Résultats de la simulation                                                                             | 38 |

| Fig. III.5. | Résultats de la simulation                                                                             | 38 |

| Fig. III.6  | .Résultats de la simulation                                                                            | 39 |

| Fig. III.7  | Résultats de la simulation                                                                             | 40 |

| Fig.III.8   | le schéma bloque de notre système                                                                      | 40 |

| Fig.III.9   | Représentation d'un signal ECG normal par matlab de la base de données                                 | 41 |

| Fig.III.10  | schéma de l'amplificateur opérationnel à deux étages                                                   | 42 |

| Fig.III.11  | Miroir de courant type NMOS et PMOS                                                                    | 43 |

| Fig.III.12  | Résistance active                                                                                      | 44 |

| Fig.III.13  | Porte de la transmission                                                                               | 44 |

| Fig.III.14  | Différentielle commentateur de type NMOS                                                               | 45 |

| Fig.III.15. | Différentielle commentateur de type NMOS avec Dummy                                                    | 45 |

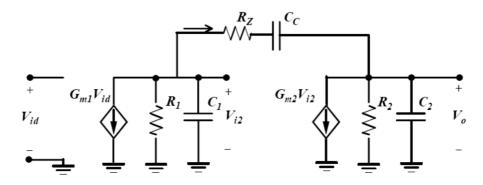

| Fig.III.16  | Petit signal Modèle simplifié de l'amplificateur opérationnel à deux étages avec le Nulling Résistance | 47 |

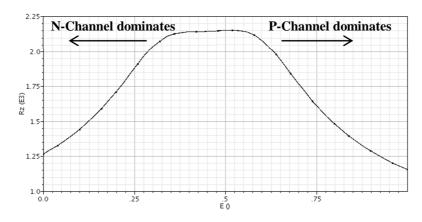

| Fig.III.17  | Résistance $R_Z$ en fonction de E                                                                      | 48 |

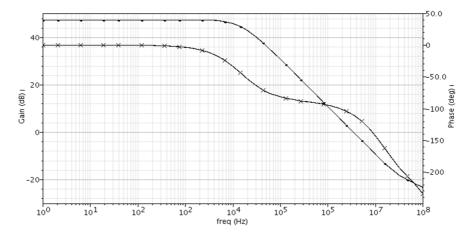

| Fig.III.18  | Montre une variation typique du gain et de phase en fonction de la fréquence.                          | 49 |

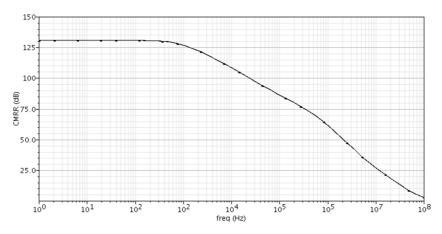

| Fig.III.19  | Montre une variation du CMRR en fonction de la fréquence                                               | 49 |

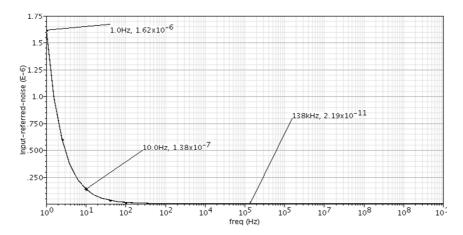

| Fig.III.20  | Montre Bruit Input-referred Noise en fonction de la fréquence                                          | 50 |

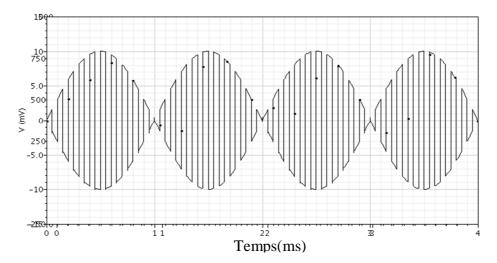

| Fig.III.21  | Sortie de signal modulé en fonction de Temps                                                           | 51 |

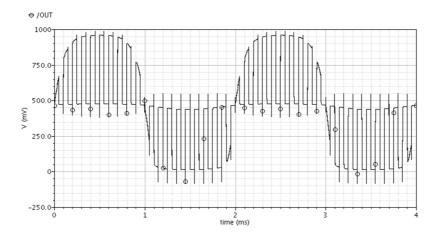

| Fig.III.22  | Montre la Sortie de l'amplificateur opérationnel en fonction de temps sans Filtre passe-bas            | 51 |

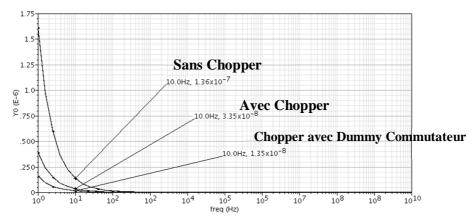

| Fig.III.23 | Montre Bruit Input-referred Noise de l'amplificateur opérationnel en fonction de la fréquence | 52 |

|------------|-----------------------------------------------------------------------------------------------|----|

| Fig.III.23 | 1 1                                                                                           | 52 |

#### Sommaire

| Introduction générale1                             | 1  |

|----------------------------------------------------|----|

| Chapitre I : Généralité sur le signal ECG.         |    |

| I.1. Introduction                                  | 3  |

| I.2. anatomie du cœur                              | 3  |

| I.3. cycle cardiaque                               | 4  |

| I.4.Genèse du signal électrique cardiaque          | 5  |

| I.5. Electrocardiogramme de surface                | 7  |

| I.6. différente ondes du signal ECG                | 7  |

| I.7. intervalles de l'ECG                          | 8  |

| I.8. conclusion                                    | 9  |

| Chapitre II : La technologie CMOS                  |    |

| II.1. Introduction                                 | 10 |

| II.2. la structure du MOSFET                       | 11 |

| II.3. caractéristique courant-tension              | 12 |

| II.4. modélisation des régimes de fonctionnement   | 13 |

| II.4.1.zone ohmique                                | 13 |

| II.4.2.zone de saturation                          | 14 |

| II.4.3.tension maximale admissible                 | 17 |

| II.5. principe de fonctionnement du transistor mos | 17 |

| II.5.1.type de transistors                         | 17 |

| II.5.1.1.mos à canal N                             | 18 |

| II.5.1.2.mos à canal P                             | 18 |

| II.6. Circuit CMOS                                 | 19 |

| II.7. miroir de courant                            | 19 |

| II.7.1.miroir de courant simple                    | 20 |

| II.7.2.montage Wilson                              | 22 |

| II.7.3.miroir de courant cascode                   | 22 |

| II.8.circuit à basse tension                       | 23 |

| II.9.Amplificateur opérationnel                    | 24 |

| II.9.a. Caractéristique d'un AOP                   | 24 |

| II.9.b. Application des Amplificateur              | 25 |

| II.9.1.Amplificateur opérationnel idéal            | 25 |

| II.9.2.Amplificateur opérationnel réel             | 26 |

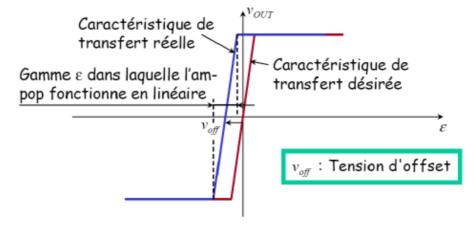

| II.9.2.a. Caractéristique large signaux              | 26 |

|------------------------------------------------------|----|

| a.1.dynamique d'entrée en mode commun                | 26 |

| a.2.dynamique de sortie                              | 26 |

| a.3.caractéristique de transfert- offset.            | 27 |

| II.10.2.b. caractéristique petit signaux             | 27 |

| b.1.impédance d'entrée-sortie                        | 27 |

| b.2.taux de réjection du mode commun-CMRR            | 28 |

| b.3.taux de réjection de l'alimentation-PSRR         | 28 |

| II.9.3.Amplificateur opérationnel CMOS à deux étages | 29 |

| II.10.bruit                                          | 29 |

| II.10.1.bruit 1/f                                    | 30 |

| II.10.2.bruit thermique                              | 30 |

| II.11.technique de réduction de bruit                | 30 |

| II.11.1.technique de stabilisation de CHOPPER        | 30 |

| II.11.2.technique auto zéro                          | 31 |

| II.11.1.1.principe de base de la technique-CHS       | 31 |

| II.12.conclusion                                     | 33 |

| Chapitre III : Simulation et Résultats               |    |

| III.1. Introduction                                  | 35 |

| III.2. miroir de courant et leurs limitations        | 35 |

| III.2.1. miroir de courant simple                    | 35 |

| a. test du miroir de courant simple                  | 36 |

| b. miroir de courant cascode                         | 36 |

| III.3. Amplificateur opérationnel à deux étages      | 40 |

| III.3.a. signal ECG                                  | 40 |

| III.3.b. Amplificateur opérationnel                  | 41 |

| III.3.b.1. Miroir de courant                         | 42 |

| III.3.b. 2.Résistance active                         | 43 |

| III.4. structure de chopper stabilisé                | 45 |

| III.5.simulation et discussion                       | 46 |

| III.3.5.a. paramètre de dispositif                   | 46 |

| III.5.b. réponse de fréquence, compensation          | 46 |

| III.5.c. taux de rejet en mode commun CMRR           | 49 |

| III.5.d. bruit                                       | 50 |

| III.5.e. circuit de chopper                          | 50 |

| Conclusion Générale                                  | 54 |

#### **Introduction générale**

Ces dernières année plusieurs nouveaux domaines émergeant en sciences et technologie sont devenus très importants dans la vie quotidienne, tels que la télécommunication, le multimédia, les applications biomédicales, etc. Ces domaines nécessitent une utilisation importante des circuits intégrés analogiques et mixtes. Tester ces derniers cause un impact considérable sur le coût de production. Ceci est dû à la complexité des circuits par leurs fonctions et leur taille qui ne cessent de s'accroitre.

Beaucoup d'efforts ont été consacrés à la réduction de la tension d'alimentation et à la réduction de la consommation des systèmes en technologie CMOS

D'un côté, les circuits intégrés numériques à basse tension d'alimentation et à faible consommation, peuvent facilement atteindre des qualités excellentes du point de vue fonctionnement (par exemple une très grande résolution et un bon rapport signal sur bruit).

De plus, la taille de la partie numérique est réduite radicalement avec la minimisation des tailles des blocs fonctionnelles.

D'un autre côté, les circuits intégrés analogiques à basse tension d'alimentation et à faible consommation avec de bonnes fonctionnalités sont très difficiles à réaliser. Par exemple, la dynamique de sortie d'un amplificateur opérationnel diminue substantiellement en réduisant la tension d'alimentation. Par ailleurs, les circuits intégrés analogiques ne peuvent pas être conçus en utilisant des tailles minimales des transistors, pour des raisons de gain de l'amplificateur, offset, bruit, etc. La surface de la partie analogique ne peut donc pas être réduite radicalement avec la minimisation des tailles des fonctions à réaliser.

Et aussi cette avancée technologique n'est pas sans risque d'où cette étude qui est basée sur l'effet de la miniaturisation sur le rendement d'un amplificateur opérationnel basse tension et qui dit miniaturisation dit nanotechnologie. Autrement dit, on a pour objectif l'étude de l'effet que pourrait avoir les différents éléments constituant un AOP à l'échelle nanométrique sur le rendement de ce dernier

Le traitement des signaux biomédicaux est devenu un outil très indispensable pour l'extraction des informations cliniques cachées dans ces signaux par exemple les signaux électro cardiographiques (ECG) vont être considérés. Ce type de signaux représente l'activité électrique du cœur enregistré par des électrodes placées sur la surface du corps.

Pour cela le présent travail sera organisé comme le suivant :

- ➤ Un premier chapitre dans lequel on parlera brièvement sur le signal ECG.

- ➤ Dans le deuxième chapitre, on va donner des généralités sur le transistor MOSFET conventionnel (introduction, structure, principe de fonctionnement, .....).on parlera aussi de la modélisation du fonctionnement d'un amplificateur opérationnel, ainsi on parlera aussi du transistor (en particulier le CMOS) qui est élément de base de l'amplificateur.

- ➤ Le dernier chapitre fournis les résultats exploités avec la simulation des circuits élémentaires, qui constituent un tel amplificateur, la simulation faite sous PSPICE et Matlab.

- > Et finalement, nous terminons notre travail par une conclusion générale.

# Chapitre 1 Généralités sur le signal ECG

#### I.1 Introduction

L'électrocardiographie (ECG) est la traduction, sous forme électrique, du fonctionnement du muscle cardiaque. L'acquisition du signal ECG indolore et non invasive, s'effectue à travers d'électrodes cutanées, convenablement réparties sur le corps humain, et sensible au potentiel électrique qui commande l'activité musculaire du cœur. Cette acquisition peut s'effectuer en milieu hospitalier ou bien de façon ambulatoire, le patient vaquant alors à ses activités quotidiennes.

Nous présentons, dans ce chapitre, le fonctionnement général du système cardiovasculaire, ses principales composantes, puis, de manière plus détaillée, le principe de l'électrocardiographie et Les caractéristiques du cycle cardiaque ainsi que son processus de propagation.

Nous abordons, également, quelques pathologies cardiaques susceptibles d'être détectées à partir du signal acquis .L'électrocardiographie est l'étude des variations de l'enregistrement de l'activité électrique des cellules cardiaques, dont dépend la contraction du cœur.

Le signal ECG enregistre les impulsions électriques qui déclenchent les contractions cardiaques. Au repos, les cellules sont chargées négativement à l'intérieur. Lors de la contraction, les cellules se dépolarisent. Ainsi, une onde progressive de stimulation traverse le cœur, entraînant la contraction du myocarde. Les ondes de dépolarisation et de repolarisation sont enregistrées sur l'ECG. Le signal graphique enregistrable est l'électrocardiogramme (ECG). Ce signal, modifié en cas d'anomalie de la commande de l'influx électrique ou de sa propagation, de la masse globale et régionale des cellules ou de leur souffrance éventuelle, donne des renseignements importants et très utilisés en médecine.

Cette présentation se limite au strict nécessaire pour une bonne compréhension de notre travail, le lecteur intéressé par une approche médicale rigoureuse pourra se reporter aux nombreux ouvrages médicaux disponibles sur le sujet comme notamment [1], [2] [3] et [4].

#### I.1 Anatomie du cœur

Le cœur est un organe contractile situé dans le thorax, entre les poumons, et permet d'assurer la circulation sanguine. Derrière le cœur se trouvent les vaisseaux les plus

importants : les deux veines caves (inférieure et supérieure), les artères pulmonaires, et l'artère aorte, comme l'illustre la figure I.1.

Le cœur est un muscle creux séparé en deux moitiés indépendantes (droite et gauche). Sa partie droite contient du sang pauvre en oxygène, et assure la circulation pulmonaire; sa partie gauche renferme du sang riche en oxygène, qui est propulsé dans tous les tissus. Chacune des moitiés comporte une oreillette et un ventricule qui communiquent par des valves d'admission (tricuspide à droite, et mitrale à gauche) qui, à l'état normal, laissent passer le sang uniquement de l'oreillette vers le ventricule. Il existe aussi des valves d'échappement qui assurent la communication entre le ventricule droit et l'artère pulmonaire (valve pulmonaire), ainsi qu'entre le ventricule gauche et l'artère aorte (valve aortique). Ces deux valves se trouvent à l'entrée de l'aorte et de l'artère pulmonaire respectivement. Les valves d'admission et d'échappement empêchent le liquide de refluer, et ne doivent jamais être ouverts en même temps sur la figure I.1 nous pouvons voir l'anatomie de cœur et des vaisseaux associés.

Les parois du cœur sont constituées par le muscle cardiaque, appelé myocarde, composé d'un ensemble de cellules musculaires cardiaques. Le myocarde est tapissé à l'intérieur par l'endocarde, et est entouré à l'extérieur par le péricarde. Les oreillettes sont séparées par le septum inter auriculaire et les ventricules par le septum inter ventriculaire. La paroi ventriculaire gauche et le septum sont plus épais que la paroi ventriculaire droite. La pompe gauche effectue le travail le plus important, car elle envoie le sang vers tous les tissus où la pression est considérablement plus grande que celle de la circulation pulmonaire pompée par le ventricule droit. Contrairement à celles des ventricules, les parois des oreillettes sont très fines.

#### I.2.Cycle cardiaque

Chaque battement du cœur entraîne une séquence d'événements mécaniques et électriques collectivement appelés cycle cardiaque. Celui-ci consiste en trois étapes majeures :

La systole auriculaire, la systole ventriculaire et la diastole. Dans la systole auriculaire, les oreillettes se contractent et projettent le sang vers les ventricules. Une fois le sang expulsé des oreillettes, les valvules auriculo-ventriculaires entre les oreillettes et les ventricules se ferment. Ceci évite un reflux du sang vers les oreillettes.

Fig.I.1Anatomie du cœur et des vaisseaux associés.

Enfin, la diastole est la relaxation de toutes les parties du cœur, permettant le remplissage passif des ventricules et l'arrivée de nouveau sang. Les phases de contractions harmonieuses des oreillettes et des ventricules sont commandées par la propagation d'une impulsion électrique. Lorsque la fréquence cardiaque change, la diastole est raccourcie ou rallongée tandis que la durée de la systole reste relativement stable.

#### I.3. Genèse du signal électrique cardiaque

Comme tous les muscles du corps, la contraction du myocarde est provoquée par la propagation d'une impulsion électrique le long des fibres musculaires cardiaques induite parla dépolarisation des cellules musculaires. En effet, le cœur comporte un réseau intrinsèque de cellules conductrices qui produisent et propagent des impulsions électriques, ainsi que des cellules qui répondent à ces impulsions par une contraction. Lors d'une activité cardiaque normale, la stimulation électrique du myocarde naît du nœud sinusal, le pacemaker naturel du cœur. Pendant la période d'activité (liée à la systole) et de repos (liée à la diastole), les

cellules cardiaques sont le siège de phénomènes électriques complexes membranaires et intracellulaires, qui sont à l'origine de la contraction.

Chaque cellule cardiaque est le siège d'échanges membranes dans lesquelles sont impliqués différents ions : le sodium Na+, le potassium K+, le calcium Ca2+ et le chlorure Cl-Les variations de potentiel observées au cours d'un cycle cardiaque, correspondent à des modifications de la perméabilité membranaire et sont liées aux échanges ioniques. Au repos, l'intérieur de la membrane cellulaire est chargé négativement par rapport à l'extérieur, pris comme référence. Cette différence de potentiel (potentiel de repos cellulaire) dépend des concentrations ioniques dans les milieux intra et extracellulaire ; pour les cellules ventriculaires, sa valeur est voisine de -90 mV (figure I.2). Quand une impulsion électrique d'amplitude suffisante agit sur une cellule excitable, l'intérieur de la cellule devient rapidement positif par rapport à l'extérieur à cause des échanges ioniques décrits par la suite. Ce processus est la dépolarisation cellulaire et est suivi par le processus de repolarisation cellulaire, c'est à dire lorsque la cellule revient à son état de repos. Les échanges ioniques qui définissent le potentiel d'action, présenté sur la figure I.2, comprend cinq (05) phases successives.

- La phase 0 ou dépolarisation rapide : Après une excitation électrique au-dessus du seuil d'activation de la cellule, un afflux rapide d'ions Na+ pénètre dans la cellule et inverse rapidement la polarité de cette dernière.

- La phase 1 ou début de repolarisation : Elle est caractérisée par une repolarisation rapide et de courte durée, due à l'inactivation des canaux Na+ et au flux sortant d'ions de potassium K+.

- La phase 2 ou repolarisation lente : Elle est due à l'entrée lente des ions Ca2+ dans la cellule, et qui atténue l'influence des canaux K+ continuant à sortir, ralentissant ainsi la phase de repolarisation.

- La phase 3 ou repolarisation : Elle correspond à la phase de repolarisation finale, etse caractérise par la fermeture des canaux ioniques spécifiques qui ramène la cellule au potentiel de repos original. Durant cette phase, les ions K+ sont toujours sortants tandis que le potentiel de la cellule tend vers son seuil de repos.

- ➤ La phase 4 ou phase de repos : Elle correspond au potentiel de repos, où la cellule est facilement excitable.

**Fig.I.2.** Les cinq phases du potentiel d'action d'une cellule du muscle myocardique, respectivement, la phase 0 correspond à la dépolarisation de la cellule, la phase 1 au début de la repolarisation, la phase 2 à la repolarisation lente, la phase 3 à la repolarisation rapide, et la phase 4 au repos.

#### I.4. Electrocardiogramme de surface

L'électrocardiogramme est la représentation graphique du potentiel électrique qui commande l'activité musculaire du cœur. Ce potentiel est recueilli par des électrodes mises à la surface de la peau. Le signal est reçu par un appareil nommé l'électrocardiographie. L'ECG se présente alors comme une suite de déflexions (ondes électrique) séparées par des intervalles, correspondant, chacune, à une phase de fonctionnement du cœur.

#### I.5. Différente ondes du signal ECG

Le signal ECG enregistre, successivement, la dépolarisation et la repolarisation auriculaires, puis la dépolarisation et la repolarisation ventriculaires. Ces phénomènes sont suivis d'un repos électrique qui correspond à la ligne de base iso électrique. Lorsque le système d'acquisition est mis en fonctionnement, apparait une succession de déflexions, séparées par des intervalles, qui ont une terminologie bien précise (figure I.3).

**Onde P**: Déflexion correspondant à la dépolarisation des oreillettes droite et gauche, d'une amplitude inférieure à 2,5 mm, et d'une durée inférieure à 0,11s.

**Complexe QRS**: Ensemble des déflexions correspondant à la dépolarisation des ventricules, sa durée doit être comprise entre 0,06s et 0,1s.

**Onde T**: Déflexion correspondante à la repolarisation ventriculaire.

**Fig. I.3** Étapes successives de dépolarisation/repolarisation du cœur qui se traduisent sur le plan électrocardiographique par différentes ondes P, QRS, et T.

#### I.6 Intervalles de l'ECG

Les différents phénomènes précédemment cités se retrouvent dans l'allure du signal électrique issu du système d'acquisition de l'ECG (figure I.4). Le signal se décompose alors comme suit :

- ➤ Intervalle PR ou PQR : Correspond au temps de conduction auriculo-ventriculaire (de début de l'onde P au début du complexe QRS), sa durée doit être comprise entre 0,12s et 0,2s.

- ➤ Intervalle ST ou RST : il séparer la fin de la dépolarisation (fin du complexe QRS) et le début de la repolarisation ventriculaire (début de l'onde T).

**Intervalle QT** : Il s'agit de la distance entre le début du complexe QRS et la fin de l'onde T, englobant la dépolarisation et la repolarisation ventriculaires.

**Intervalle RR** : Cet intervalle désigne le temps entre deux ondes R successives. La facilité de la détection de l'onde R donne l'importance de cet intervalle qui sert à mesurer la fréquence cardiaque.

**Fig. I.4** Étapes successives de dépolarisation/repolarisation du cœur qui se traduisent sur le plan électrocardiographique par différentes ondes P, QRS, et T.

#### I.7. Conclusion

L'électrocardiographie est une technique largement utilisée, elle remplit bien sa fonction et fourni de façon fiable un signal auquel nous pouvons appliquer des méthodes appropriées du traitement de signal. Ce chapitre a pour but de sensibiliser le lecteur à l'importance d'étudier les différentes caractéristiques du signal ECG, tels que les amplitudes des ondes P, Q, R, S et T ,leurs formes, leurs durées ainsi les intervalles qui les séparent afin de faire un bon diagnostic.

## Chapitre 2 La technologie CMOS

#### II.1.Introduction

L'électronique et l'informatique ont accompli d'énormes progrès en un temps record [4]. En moins de soixante ans, les dispositifs ont subi de profondes modifications. Ainsi, les lampes triodes originelles de dimensions macroscopiques (Figure. II.1-a) ont été remplacées par des transistors MOSFET ne mesurant actuellement que quelques dizaines de nanomètres de longueur de grille.

**Fig. II.1.** Évolution de la technologie : de la lampe triode (a) au MOSFET nanométrique vue en microscopie

De nos jours, grâce aux microordinateurs, une même opération élémentaire est effectuée un million de fois plus rapidement, et consomme 100000 fois moins de puissance électrique. Cette évolution repose sur la filière silicium avec comme figure de proue le transistor à effet de champ à grille isolée dit MOSFET (Métal Oxyde Semi-conducteur Field Effect Transistor) combiné à la technologie CMOS (Complementary Métal Oxyde Semi-conducteur). Ainsi que l'illustre la Fig. I.2, à partir du milieu des années 70, avec l'avènement des microprocesseurs et de la micro-informatique, le nombre de MOSFET par puce n'a pas cessé de croître. Cette croissance s'est faite grâce à la diminution des dimensions des transistors et notamment la longueur de la grille L. En 1965, Gordon Moore prédit que le nombre de transistors par unité de surface doublerait tous les ans.

L'évolution de la technologie CMOS actuelle a pour but de concevoir des Transistors et par conséquence des circuits intégrés dans les échelles submicronique Cette réduction d'échelle a concerné évidement les dimensions de la zone active du Transistor MOSFET. La miniaturisation s'accompagne indéniablement d'effets indésirables appelés effets canaux courts (SCE) qui viennent s'ajouter à la difficulté de la réalisation de ces dispositifs de petites dimensions. L'apparition des nouveaux procédés de fabrication notamment la photolithographie a donné naissance à de nouvelles architectures pour les transistors

MOSFETs avec une orientation verticale du canal. Ce procédé a permis entre autre, un meilleur contrôle des effets canaux courts [5].

**Fig. II. 2.** Illustration de la loi de Moore : évolution du nombre de transistors dans les microprocesseurs Intel

#### II.2.La structure du MOSFET

Avant de présenter les équations permettant le calcul du courant de drain du transistor MOS, il est nécessaire de définir les différentes notations utilisées [6].

Fig. II.3. Vue schématique du transistor MOS de type N

Schématiquement un transistor MOSFET est constitué de [7] :

➤ l'électrode de grille : C'est l'électrode qui va commander le dispositif tel un interrupteur. Dans les technologies actuelles (jusqu'au nœud technologique 45nm), elle est constituée de silicium poly cristallin, souvent appelé poly silicium, qui est dopée selon s'il

s'agit d'un nMOSFET ou d'un pMOSFET, respectivement N+ et P+. Cette électrode est isolée du substrat par le diélectrique de grille. Il s'agit d'oxyde de silicium nitruré : SiON.

➤ Le canal : C'est la zone constituée de silicium monocristallin, située sous l'oxyde de grille et qui constitue le lieu de conduction des porteurs minoritaires. Elle est dopée P dans le cas d'un nMOSFET, et N pour un PMOSFET. .

➤ Le module de jonctions et extensions : Il s'agit des zones de source et de drain, également noté S/D, qui sont les électrodes latérales. Elles sont réalisées par dopage à dégénérescence du substrat, N+ dans le cas NMOSFET et P+ pour le PMOSFET. Nous distinguons deux zones : au contact direct du canal nous trouvons les extensions, ou LDD (de «Lightly Doped Drain »), où le dopage est plus superficiel. Puis de part et d'autre viennent les deux zones ohmiques de source et de drain, avec des jonctions plus profondes pour réduire leur résistivité ; elles sont formées après la création des espaceurs qui sont en nitrure (Si3N4) dans les technologies actuelles, Les électrodes de grille, de drain et de source sont siliciurées (réaction chimique d'un métal avec le silicium) afin de réduire la résistance de la prise de contact. Dans les nouvelles technologies elles sont faites avec du siliciure de nickel (NiSi).

#### II.3. Caractéristiques courant-tension

Ces caractéristiques, encore appelées caractéristiques statiques, sont celles que l'on peut relever en courant continu ou à basse fréquence. Les caractéristiques dynamiques, tant en amplification qu'en commutation seront aussi évoqué par la suite.

Comme pour les transistors bipolaires, on trace un réseau de courbes ID = f (VDS) paramétrées en VGS (pour les transistors bipolaires on trace Ic = f (VCE) paramétré en IB). On remarque que ce réseau de caractéristiques comporte trois régions (voir figure I.7) : La région de blocage ou le cut off, pour VGS <Vth

La région de fonctionnement en triode (appelée ainsi par similitude avec les caractéristiques d'un tube triode) correspondant à un fonctionnement du canal avant pincement.

La région dite « de saturation du courant drain » correspondant à un fonctionnement "pincé".

Fig. II.4. Caractéristiques d'un transistor MOSFET à canal N. [7]

On note que le fonctionnement du transistor MOSFET dans la zone de saturation, correspond au fonctionnement en amplification. Pour un fonctionnement en commutation, le MOSFET sera : soit bloqué (interrupteur ouvert), soit utilisé dans la zone triode où il se comporte comme une résistance (interrupteur fermé).

Pour le transistor à canal P, le fonctionnement est identique à celui du canal N, les tensions VGS et VDS sont simplement négatives et le courant circule de la Source vers le Drain. Le canal P est formé par accumulation de trous.

#### II.4. Modélisation des Régimes de fonctionnement [8]

#### II.4.1.Zone Ohmique

La caractéristique le courant Id en fonction de la tension Vds peut être approximée par la relation

$$I_D = K(2(V_{GS} - V_{th})V_{DS} - V_{DS}^2)$$

(II. 1)

Où K est un paramètre dépendant de la géométrie et de la technologie utilisée

$$K = \frac{1}{2}\mu_e C_{ox} \frac{W}{L} \tag{II. 2}$$

Avec :  $\mu e$  : mobilité de l'électron, Cox : capacité grille-substrat par unité de surface, L : Longueur du canal, W : Largeur du canal.

Si la tension drain-source est suffisamment faible (cas du fonctionnement avant pincement) le terme  $V_{DS}^2$  peut être négligé, on obtient alors:

$$I_D = K(2(V_{GS}-V_{th})V_{DS}-V_{DS}^2)$$

(II. 3)

Cette relation linéaire entre ID et VDS montre que le MOS se comporte comme une résistance dont la valeur peut être contrôlée par VGS.

$$R_{DS} = [K(2(V_{GS}-V_{th})V_{DS}-V_{DS}^{2})]^{-1}$$

(II. 4)

#### II.4.2. Zone de Saturation : Fonctionnement en amplificateur

La zone de fonctionnement à courant Drain saturé correspond au pincement du canal qui se produit pour VDS = VGS - Vth.

En remplaçant VDS par cette valeur dans l'expression (I.1) on obtient :

$$I_D = K(2(V_{GS}-V_{th})(V_{GS}-V_{th}) - (V_{GS}-V_{th})^2$$

(II.5)

$$I_D = K(V_{GS} - V_{th})^2 (II.6)$$

Dans cette zone, le courant du drain est totalement indépendant de la tension drainsource VDS. Il suit l'évolution de la tension grille-source VGS selon une loi quadratique. Dans ce cas, on peut dire que le MOSFET se comporte comme une source de courant idéale dont la valeur est contrôlée par la tension grille-source VGS. On en déduit le modèle du fonctionnant en amplification ci-après :

Fig. II.5. Schéma équivalent grands signaux d'un MOSFET

On notera que la ligne de partage entre la zone triode et la zone de saturation correspond au pincement du canal qui se produit pour

$$VDS = VGS - Vth$$

En reportant dans la relation (I.7) on obtient l'équation de cette ligne :

$$I_D = K(V_{DS})^2 \tag{II.7}$$

Nous avons supposé que toute augmentation de VDS au-delà de la valeur pour laquelle se produit le pincement était sans effet sur le courant Drain. Ainsi, à mesure que la tension VDS augmente, le point de pincement se déplace légèrement en direction de la source. La longueur effective du canal se trouve donc réduite. Ce phénomène est connu sous le nom de modulation de la longueur du canal. Ce phénomène est modélisable par l'équation suivante :

$$I_D = K(V_{GS} - V_{th})^2 (1 + \lambda V_{DS})$$

(II.8)

Où λ est une constante dépendant du MOSFET utilisé.

La figure ci-dessous montre un réseau de caractéristiques du MOSFET, tenant compte de cet effet.

Fig. II.6. Résistance de sortie du MOSFET [8]

On note que tous les segments de droite, de la caractéristique  $I_{DS}$ – $V_{DS}$ , se coupent sur l'axe des VDS en un point d'abscisse

$$V_{DS} = -\frac{1}{\lambda} = -V_A \tag{II.9}$$

Avec VA un paramètre valant typiquement de 200 à 300V. Dans ce cas, on pourra déduire que la résistance de sortie d'un MOSFET fonctionnant en saturation est finie et peut s'exprimer :

$$R_0 = \left(\frac{\partial I_D}{\partial V_{DS}}\right)^{-1} \tag{II. 10}$$

D'après l'équation I.8 et pour VGS constant on a:

$$R_0 = [\lambda K (V_{GS} - V_{th})^2]^{-1}$$

(II. 11)

En négligeant le terme \( \lambda VDS \) que l'on peut approximer par

$$R_0 = (\lambda I_D)^{-1} (II. 12)$$

Où Id est le courant correspondant à la valeur particulière de VGS pour laquelle Ro est évaluée. Cette relation peut aussi s'écrire sous la forme:

$$R_0 \approx \frac{V_A}{I_D} \tag{II.13}$$

La résistance de sortie Ro est inversement proportionnelle au courant de polarisation ID. delà on pourra déduire le schéma équivalent grand-signaux ci-dessous.

Fig. II.7. Schéma équivalent grands signaux du MOSFET

#### II.4.3. Tension maximale admissible

Lorsqu'on augmente la tension Drain-Source VDS, le champ électrique à la jonction PN Drain-Substrat (qui est relié à la source) s'élève, et on atteint la tension d'avalanche. Pour éviter d'atteindre ce phénomène dangereux pour le composant, le constructeur spécifie la tension Drain-Source maximale à ne pas dépasser.

Afin d'éviter l'accumulation de charges statiques dans le condensateur grille-substrat qui pourraient provoquer un perçage de l'oxyde extrêmement fin servant de diélectrique, des diodes de protection intégrées limitent la tension grille-source. La tension maximale grille-source VGSmax est spécifiée par le constructeur.

#### II.5. Principe de fonctionnement du transistor MOS

Le principe de fonctionnement du MOSFET est comparable à celui d'un interrupteur. En effet, son fonctionnement est basé sur la modulation du transport d'une densité de charges dans le canal de conduction par le biais d'un champ électrique qui lui est appliqué perpendiculairement. La création des porteurs de charge (électrons pour un transistor N MOS, trous pour un transistor P MOS) par effet de champ est régi par la polarisation Vg la grille. Le transport des porteurs dans le canal se fait sous l'impulsion d'une différence de potentiel

Vd entre deux réservoirs de charges (source et drain) établissant un courant de drain Id

Le transistor assure donc la transition d'un état bloqué (Vg= 0V) pour lequel le courant de drain équivaut au courant de fuite Ioff, à un état passant pour lequel la polarisation de grille Vg est égale à celle de drain Vd(Vg=Vd=Vdd)permettant le passage du courant de drain Ion Le passage du premier état au second est effectif lorsqu'un nombre suffisant de porteurs est présent dans le canal, c'est à dire quand une tension de grille Vg supérieure à la tension dite de seuil (Vth) est appliquée.

#### II.5.1. Types de Transistors

Selon le type de semi-conducteur constituant le Substrat, on peut distinguer deux types de transistors ; les transistors NMOS ou transistor a canal N conçu un substrat de type p dits NMOSFET et transistor PMOS ou transistor MOS a canal P conçu un substrat de type n dits PMOSFET.

#### II.5.1.MOS à canal N

Dans le cas des NMOS la grille est polarisée par une VGB positive, afin de créer une zone de déplétion peuplée d'électrons à l'interface SC/Isolant. La source et le drain sont reliés par un canal formé d'électrons. La différence de potentiel entre le drain le source qu'on l'appelle *VDS* et positive, le sens du courant se fait la source vers le drain.

Fig. II.8. Transistor MOS à canal N

#### II.5.2.MOS à canal P

Pour les transistors à canal P la grille est négativement polarisée, la zone de déplétion à l'interface SC/Isolant est peuplée par des trous, le canal de conduction est formé de trous et la tension *VDS* doit être négative pour drainer ces trous. Le courant circule dans le même sens du déplacement des trous soit alors de la source vers le drain.

Fig. II.9. Transistor MOS à canal P

#### **II.6.Circuit CMOS**

La technologie CMOS est une technologie planaire destinée au développement des systèmes à très large échelle d'intégration (VLSI & ULSI). Grâce aux propriétés des transistors MOSFET complémentaires (notées CMOS pour Complementary Métal Oxyde Semi-conducteur), cette technologie permet de réaliser des circuits à faible coût et à basse consommation d'énergie. Cet avantage lui a permis d'être reconnue comme la technologie de pointe la plus avancée et la plus maîtrisée dans le domaine de la microélectronique.

Parmi les types de technologies CMOS, on peut citer les trois qui sont les plus connues:

- La technologie CMOS à caisson N: Une technologie CMOS à caisson N utilise un substrat en silicium de type P dans lequel un caisson de type N est diffusé. Des transistors MOSFET à canal P sont alors réalisés dans ce caisson et des MOSFET à canal N sont réalisés dans le substrat

- La technologie CMOS à caisson P: Une technologie CMOS à caisson P permet de réaliser les transistors de type P sur le substrat de type N et des transistors de type N dans le caisson P.

- La technologie CMOS à double caisson : La technologie CMOS à double caisson utilise un substrat en silicium de type quelconque, sur lequel sont déposés des caissons de type N et des caissons de type P.

Les transistors N-MOSFET et P-MOSFET fabriqués par ces technologies sont utilisés pour réaliser des fonctions analogiques ou numériques.

#### II.7.Miroir de courant

Les miroirs de courant sont des circuits très utilisés dans la conception des circuits analogiques CMOS, ils sont utilisés pour multiplier ou diviser le courant. Le miroir de courant utilise le principe qui dit que : si les potentiels grille –source de deux transistors MOS identiques sont égaux, alors les courants qui traversent leurs canaux sont égaux.

Un miroir de courant est un élément avec au moins trois terminaux, comme montré dans figure. (II.10), le terminal commun est connecté à la masse, le courant d'entrée est connecté au générateur de courant idéal. Le courant de sortie est égal au courant d'entrée multiplié par le gain désiré. Si le gain est unité, le courant d'entrée est reflété à la sortie.[9]

Fig. II.10 : Le schéma de principe d'un miroir de courant

Les miroirs de courants sont utilisés dans les circuits intégrés analogiques comme des éléments de polarisation et comme des dispositifs de charge pour les étages de l'amplificateur. L'usage des miroirs de courants en polarisation peut avoir pour résultat l'insensibilité supérieure de la performance du circuit aux variations de l'alimentation et de la température. Les miroirs de courants occupent moins d'espace que les résistances lorsque la région du die exigée pour fournir le courant de polarisation est petite. Quand il est utilisé comme un élément de charge dans l'amplificateur.

Il existe différents types de miroirs de courant tels que :

#### II.7.1.Miroir de courant simple

Fig. II.11 Miroir de courant simple à 2 MOS

#### **Fonctionnement**

Le transistor M1 (figure II.11) est en saturation ( $V_{DS_1}=V_{GS_1}$ )

Supposons que  $V_{DS_2} \ge V_{GS} - V_{TH}$

$V_{S2}$  est plus grand que  $V_{T2}$ . Cette affirmation permet l'utilisation des équations du transistor MOS dans la région de saturation. Dans le cas général, le rapport  $I_2$  / $I_1$ est donné par l'équation (II.14):

$$\frac{I_2}{I_1} = \left(\frac{L_1 W_2}{L_2 W_1}\right) \left(\frac{V_{GS2} - V_{T2}}{V_{GS1} - V_{T1}}\right)^2 \left(\frac{1 + A V_{DS2}}{1 + A V_{DS1}}\right) \left(\frac{\mu_{02} C_{0x2}}{\mu_{01} C_{0x1}}\right)$$

(II.14)

Les composants d'un miroir de courant sont pressés dans le même circuit intégré, les paramètres physiques tels que  $V_{th}$ , $\mu_0$ , $C_{ox}$ , sont identiques pour les deux transistors

Nous pouvons donc simplifier la première équation par :

$$\frac{I_2}{I_1} = \left(\frac{L_1 W_2}{L_2 W_1}\right) \left(\frac{1 + A V_{DS2}}{1 + A V_{DS1}}\right) \tag{II.15}$$

$siV_{DS2} = V_{DS1}$ , le rapport devient :

$$\frac{I_2}{I_1} = \left(\frac{L_1 W_2}{L_2 W_1}\right) \tag{II.16}$$

Par conséquent. Le gain d'un miroir de courant est directement dicté par les dimensions des deux transistors

L: la longueur du canal.

W: la largeur du canal.

$\mu_0$  La mobilité des porteurs de charges à faible champ.

$\delta$ : paramètre de modulation de la longueur de canal qui peut être considéré comme l'inverse de la tension d'Earl.

#### II.7.2.Montage WILSON

Fig. II.12 Miroir de courant WILSON

#### **Fonctionnement:**

Les transistors T1, T2 et T3 sont connectés de manière à présenter une contre-réaction. Lorsque l'on applique un courant à l'entrée, le transistor T3 conduit et une tension UGS1 apparaît aux bornes de T1 et T2. Lorsque l'on cherche à augmenter de façon externe le courant de sortie, la tension UGS1 augmente, ce qui a pour effet de baisser le potentiel de grille de T3 qui conduit moins et stabilise ainsi le courant de sortie. Le calcul à l'aide ce modèle permet de montrer que l'impédance de sortie de cette source de courant est nettement plus élevée (facteur mille environ) que celle du simple miroir Figure II.12.

#### II.7.3.Miroir de courant cascode

Les miroirs simples posent des problèmes en raison de leur faible résistance de sortie. Donc la résistance de sortie doit être utilisée la plus grand possible c'est pourquoi, le plus généralement, les sources de courant sont réalisées avec des miroirs de courant cascode figure [13].

#### **Fonctionnement**

Le courant d'entrée est imposé, donc le potentiel de drain de T4 ne dépend que des tensions UGS1, UGS2 et UGS3. Comme ces tensions dépendent principalement du courant d'entrée, le potentiel de drain de T4 reste constant ainsi que le courant qui le traverse.

Fig. II.13Miroir de courant cascode

#### II.8 Circuit à basse tension[10]

Le terme « basse tension » est utilisé pour désigner les circuits capables de fonctionner à des tensions d'alimentation comprises entre 1 et à 5volts. Ces basses tensions d'alimentation induisent le nombre maximum de tension grille-source et de tension de saturation qui peuvent être assemblés en série.

Dans le cas des circuits CMOS, la réduction des tensions d'alimentation se justifie par le fait que la technologie se dirige vers des tailles submicroniques (même nanométriques), donc l'épaisseur de l'oxyde des composants MOS décroît en conséquence. Pour éviter des ruptures de jonctions p-n, l'intensité du champ électrique doit être réduite. De plus, comme la longueur du canal est réduite à des échelles submicroniques et que l'épaisseur grille-oxyde n'est plus que de quelques nanomètres, la tension d'alimentation doit être réduite pour assurer la fiabilité des composants.par exemple ,un processus standard à 0.8 µm peut résister à une tension d'alimentation maximum subie de environ 5 volts, mais les composants conçus à

l'aide d'une méthode CMOS à  $0.5\mu m$  ne peuvent tolérer qu'environ 3.5 volt actuellement, des dimensions de  $0.35\mu m$ ,  $0.25\mu m$ ,  $0.18\mu m$  et même les 90nm sont atteintes .la tension d'alimentation maximale et réduira jusqu'à 1.8v et même 0.5 v.

#### II.9.Amplificateur opérationnel[12]

Un amplificateur opérationnel(aussi dénommé ampli-op ou ampli op, AOP, ALI(Amplificateur Linéaire Intégré) ou AIL) : c'est un amplificateur électronique qui amplifie une différence de potentiel électrique présente à ses entrées. Il a été initialement conçu pour effectuer des opérations mathématiques dans les calculateurs analogiques : il permettait de modéliser les opérations mathématiques de base comme l'addition, la soustraction, l'intégration, la dérivation et d'autres. Par la suite, l'amplificateur opérationnel est utilisé dans bien d'autres applications comme la commande de moteurs, la régulation de tension, les sources de courants ou encore les oscillateurs.

Physiquement, un amplificateur opérationnel est constitué de transistors, de tubes électroniques ou de n'importe quels autres composants amplificateurs. On le trouve communément sous la forme de circuit intégré.

Un AOP dispose au minimum de deux entrées, de deux broches d'alimentation et d'une sortie. L'entrée notée V+ est dite non-inverseuse tandis que l'entrée V- est dite inverseuse en raison de leur rôle dans les relations entrée/sortie de l'amplificateur. La différence de potentiel entre ces deux entrées est appelée tension différentielle d'entrée.

#### Caractéristique d'un AOP

Les AOP ont pratiquement tous la même structure interne. Ce sont des circuits monolithiques dont une puce de silicium constitue le substrat commun.

L'amplificateur différentiel en entrée → étage adaptateur d'impédance → amplificateur de sortie.

Toutes les liaisons sont directes. Ils sont alimentés par des tensions continues symétriques ; variant de  $\pm 2.5$ V à  $\pm 24$ V (une valeur typique est de 15V). Ils sont caractérisés par :

- Gain en tension très important  $10^5$  à  $10^7$

- Impédance d'entrée très grande  $10^5$  à  $10^{12} \Omega$

- Impédance d'entrée en mode commun très grande  $10^8$  à  $10^{12}$   $\Omega$

- Impédance de sortie faible 10 à 500  $\Omega$

- Produit gain-bande passante peut dépasser 100MHz

#### **Applications des amplificateurs**

#### > Amplificateur linéaire

Amplificateurs de précision

Amplificateurs à gains programmables

Amplificateurs faible consommation

Amplificateur de puissance

Amplificateur à collecteur ouvert

Ampli d'isolement, etc. . .

#### > Amplificateur non-linéaire

Convertisseur Numérique \$ Analogique

Fonction logique (NOR, NAND. . .

Mise en forme des signaux, horloge, astables. . .

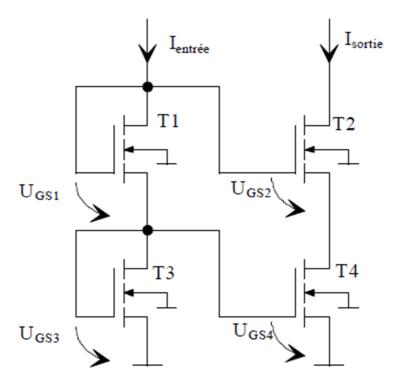

#### II.9.1.Amplificateur opérationnel idéal

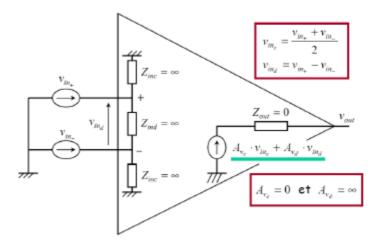

Fig. II.14. Schéma d'un Amplificateur opérationnel idéal

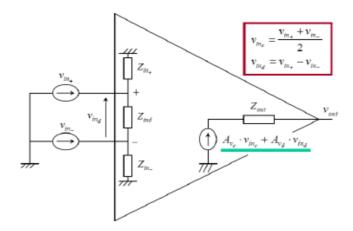

L'amplificateur opérationnel idéal est un système linéaire à deux entrées et une sortie amplifiant infiniment la différence des signaux d'entrée et rejetant parfaitement leur somme (mode commun) figure II.14.

Avd=  $\infty \Rightarrow V$  ind=  $\varepsilon = 0$

D'autre part, ses impédances d'entrée (de mode commun Zinc et de mode différentiel Zind) sont infinies; son impédance de sortie est nulle.

- 1) Comme tout système linéaire réel, l'amplificateur opérationnel travaille autour d'un point de polarisation. En général, il est alimenté de manière symétrique (+VDD, -VDD) de telle sorte que son point de polarisation en sortie, VOUT0, soit nul. De même pour les entrées positive et négative, «elles varient autour de 0V».

- 2) Comme tout système réel, l'amplificateur est limité par des phénomènes larges signaux (l'amplificateur ne répond plus de manière linéaire) et par sa bande passante (réponse de l'amplificateur en petits signaux)

# II.9.2. Amplificateur opérationnel réel[10]

#### Caractéristiques larges signaux

## > Dynamique d'entrée en mode commun

La dynamique d'entrée en mode commun est définie comme la gamme de tension VINC sur laquelle peut varier la tension de mode commun sans que les caractéristiques de l'amplificateur opérationnel ne soient notablement dégradées. En particulier, le gain différentiel doit rester très élevé (infini) et le gain de mode commun rester très faible (nul).

N.B.: En particulier, le mode commun est rejeté sur toute la dynamique d'entrée en mode commun

## **Dynamique de sortie**

A l'instar de la dynamique d'entrée en mode commun, la dynamique de sortie est définie comme la gamme de tension sur laquelle la sortie peut varier sans que les caractéristiques de l'amplificateur opérationnel ne soient notablement dégradées. En particulier, le gain différentiel doit rester élevé.

## Caractéristique de transfert – Offset

Fig. II.15 Caractéristique de transfert - Offset

## Caractéristiques petits signaux[6]

#### Impédances d'entrée - Impédances de sortie

L'amplificateur comportant deux nœuds à l'entrée et un nœud à la sortie, les impédances peuvent être définies comme suit :

Fig. II.16 Schéma d'un Amplificateur opérationnel réel

L'impédance d'entrée en mode commun vaut alors :

$$Z_{inc} = \frac{Z_{in_{+}} \cdot Z_{in_{-}}}{Z_{in_{+}} + Z_{in_{-}}}$$

(II.17)

## Marge de phase

Plutôt que de travailler avec le coefficient d'amortissement, le concepteur de CI préfère travailler avec la marge de phase (du système en boucle ouverte).

#### Définition

La marge de phase d'un système correspond au déphasage supplémentaire négatifqu'il faut ajouter au signal de sortie pour qu'il présente un déphasage de -180à la fréquence unitaire (fréquence pour laquelle le gain vaut 1 ou 0dB)

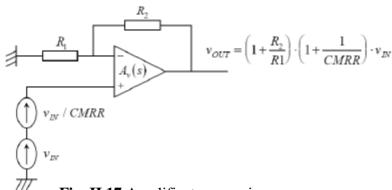

## > Taux de réjection du mode commun – CMRR

Il est défini par le rapport du gain en mode différentiel sur le gain en mode commun.

$$CMRR = \frac{A_{v}}{A_{v}} (II.18)$$

Fig. II.17 Amplificateur non inverseur

Dans un montage amplificateur non inverseur, le CMRR dégrade la précision du gain d'amplification. Dans un montage inverseur, le mode commun est nul et n'influe donc pas sur le gain du système.

## > Taux de réjection de l'alimentation – PSRR

On définit le PSRR comme le rapport du gain entre la sortie et l'alimentation sur le gain différentiel. Si l'amplificateur est alimenté par deux tensions symétriques, VDD et VSS, on définit deux PSRR

$$PSRR_{vdd} = \frac{A_{v}}{v_{out}/v_{odd}}$$

(II.19)

et

$$PSRR_{vss} = \frac{A_{v_d}}{V_{out}/V_{cs}}$$

(II.20)

## II.9.3.Amplificateur opérationnel CMOS à 2 étages

L'architecture interne d'un AOP CMOS est donnée dans la figure II.18. Il est constitué de deux étages : une paire différentielle et un amplificateur source commune. La capacité Cc a été ajoutée pour des questions de stabilité.

En général, la vitesse de balayage (slew rate) est limitée par le temps nécessaire aux courants de polarisation des divers étages de l'amplificateur opérationnel pour charger et décharger les capacités du circuit. Le slew-rate est donc constant (charge ou décharge d'une capacité à courant constant) et s'exprime en V/ms.

Fig. II.18. Architecture interne d'un AOP CMOS

#### II.10.Bruit

Les applications moderne de la technologie CMOS imposent une modélisation correcte du bruit afin d'assurer un bon fonctionnement. On a deux sources de bruit sont généralement considérée pour le transistor CMOS. La première est une source de bruit thermique ayant pour origine la nature résistive (non linéaire) du canal. La seconde est une source de bruit de scintillation (bruit 1/f) dominant en basses fréquences et ayant comme principale origine les défauts d'interfaces entre la grille et le canal. Ces deux sources n'étant pas corrélées, la densité spectrale correspondant est la somme des deux composantes respectives :

$$S_{br} = S_{th} + S_{1/f}.$$

(II.21)

#### II.10.1. Bruit en 1/f

Ce bruit est sensiblement plus grand dans les transistors mos en comparaison avec les bipolaires ou il est principalement conditionnée par l'état d'interface a la jonction constitué par la couche d'oxyde de grille et le canal de conduction, ce bruit est gênante dans les applications de basses fréquences. Il est attribué a des inhomogénéités, des disparités de l'interface SI/SIO<sub>2</sub> mais son origine est encore mal cernée.

#### II.10.2. Bruit thermique

le bruit thermique ou bruit de Johnson est dû principalement a l'agitation thermique des porteurs décharge, dans un transistor mos ce bruit est modalisé par la densité spectrale du courant circulant dans le canal du drain vers la source .lorsque la tension entre le drain et la source est nulle .le canal est traité comme étant une résistance homogène, d'après le théorème de nyguist ,la densité spectrale du courant associé au bruit thermique ,id est donnée par :

$$Id^2=4.k.T.G_0$$

(II.22)

ou K: la constant de Boltzman.

T : la température absolue.

$G_0$ : la conductance du canal pour vds=0.

## II.11. Technique de réduction du bruit

Ce travail porte sur l'étude d'un amplificateur entièrement intégré en technique CMOS dédié à des applications hautes précisions en basses fréquences. L'un des inconvénients de la technologie CMOS par rapport à la technologie bipolaire est son bruit de basse fréquence (ou bruit en 1/f) qui est beaucoup plus important. Quelques techniques de dimensionnement des grandeurs caractéristiques du bruit et de l'offset furent proposées telles que l'AUTOZERO et la technique CHOPPER. Bien que ces méthodes soient déjà bien connues et utilisées, une grande confusion quant à leurs effets sur le bruit large bande persiste. L'un des objectifs de ce travail est de distinguer et de mettre en valeur les qualités et les défauts inhérents à chacune de ces techniques.

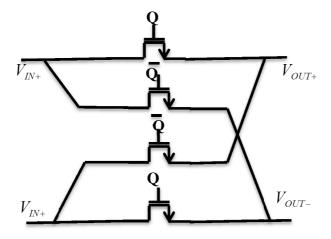

# II.11.1.Technique de stabilisation chopper (C.H.S) [13]

L'amplificateur « chopper » est considéré comme l'élément clé de la conception des cartes d'acquisition puisqu'il possède une meilleur réduction du bruit .En pratique il est destiné à des applications d'instrumentation dans différents domaines tel que le biomédical et

l'optoélectronique. Cette méthode tire profit d'une technique de modélisation qui n'augment pas le bruit à large bande ni le bruit blanc à bande étroite .ainsi la CHS est une méthode très pertinent pour le traitement des signaux en temps réel tel que la surveillance des activités neuromusculaires.

# II.11.2.Technique auto zéro

Le principe de la méthode "auto zéro "consiste à échantillonner et d'enregistrer le bruit et l'offset de l'amplificateur. Ces valeurs seront ensuit soustraites des valeurs instantanées de ces mêmes grandeurs, ainsi les composantes indésirables seront largement éliminées. L'échantillonnage de bruit a pour effet secondaire d'augmenter la composante de bruit blanc résiduelle à cause de phénomène de repliement .cette technique sera donc plutôt appliquée a des circuits déjà échantillonnées où le repliement du bruit est de toute façon inévitable .

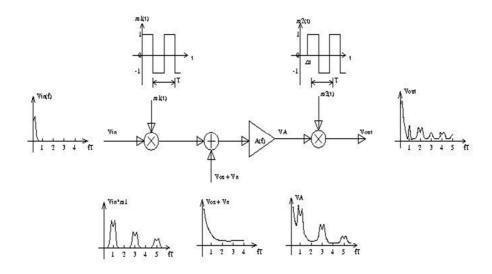

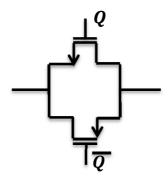

## II.11.1.1. Principe de base de la technique-CHS:

La technique CHS est basé sur le principe de modulation AM; une porteuse haute fréquence m1(t) module un signal informatif basse fréquence avant d'être entaché par le bruit dû aux composants constituants le modulateur. Le principe de cette technique est clairement illustré dans la Figure II.19. Avec une entrée ev\_in, une sortie V\_out sortie, et un gain linéaire « A ». Aussi, VOS et VN désignent le décalage DC et le bruit déterministe respectivement. Il est supposé que le signal d'entrée est à bande limitée ( à la moitié de la fréquence de découpage f\_chop ) si aucun signal repliement ne se produit [9][10]. Le rôle de l'amplificateur sélectif de gain « A », centré sur la fréquence du modulateur, est d'amplifier le signal issu du modulateur et d'éliminer le spectre du bruit qui s'étend sur la gamme basse fréquence. Le signal récupéré à la sortie de l'amplificateur subira par la suite une démodulation suivie d'un filtrage passe bas, dans le but d'extraire le signal informatif. Si le spectre du signal d'entrée est limité à la moitié de la fréquence chopper (c'est à dire la fréquence de porteuse), aucun chevauchement de signal ne se produira (Vérification de la condition de Shannon)  $f_{echant} \ge 2.f_{max}$ .

$\mathbf{v_{in}}$  (t) : signal informatif.

$\mathbf{m_1}(t)$ : la porteuse.

**m**<sub>2</sub>(t):Signal du démodulateur.

$\mathbf{v_{os}}(t)$ : l'offset.

$\mathbf{v}_{\mathbf{n}}(\mathbf{t})$ : signal du bruit.

$\mathbf{v}_{\text{out}}(\mathbf{t})$ : signal de sortie.

v<sub>A</sub>:Signal amplifié.

Figure II.20. Schéma principale de la technique CHS.

Aussi, Cette méthode tire profit d'une technique de modulation qui n'augmente pas le bruit à large bande ni le bruit blanc à bande étroite. Ainsi la CHS est une méthode très pertinente pour le traitement des signaux en temps réel, tel que la surveillance des activités neuromusculaires La décomposition en série de Fourrier du signal  $m_1(t)$  donne :

$$M_1(t) = 2\sum_{k=1}^{\infty} \frac{\sin(\frac{k\pi}{2})}{(\frac{k\pi}{2})} \cos(2\pi f_{chop}kt)$$

(II.23)

Ses k<sup>ièmes</sup> coefficients de Fourier, Mk, ont la propriété:

$$M_0 = M_{\pm 2} = M_{\pm 4} \dots = 0.$$

(II.24)

Le spectre du produit du signal informatif et le signal de la porteuse est schématisé dans la figure III.1. Après amplification le signal est démodulé par  $m_2(t)$ , on obtient par multiplication la formule:

$$V_d(t) = 4AV_{in}(t)\sum_{k=1}^{\infty} \frac{sin\left(\frac{k\pi}{2}\right)}{\left(\frac{k\pi}{2}\right)}cos\left(2\pi f_{chop}kt\right)\sum_{k=1}^{\infty} \frac{sin\left(\frac{k\pi}{2}\right)}{\left(\frac{k\pi}{2}\right)}cos\left(2\pi f_{chop}kt\right) (\text{II}.25)$$

$\checkmark$  L,k: nombres entiers

$\checkmark$   $V_d(t)$ : signal démodulé

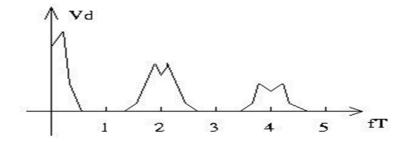

La figure II.21 représente la transformée de Fourier de ce signal de sortie démodulé.

Fig. II.21. Transformée de Fourier du signal de sortie idéal sans bruit.

Pour récupérerez signal d'origine sous forme amplifiée, le signal modulé est appliqué à un filtre passe-bas avec une fréquence de coupure légèrement supérieure à la largeur de bande du signal d'entrée ,dans ce cas ,la moitié de la fréquence de découpage. Le bruit ainsi que le décalage DC sont modulés qu'une seule fois .SiS $_N(f)$  désigne la densité spectrale de puissance(PSD) du bruit et le décalage DC, le PSD de( $V_{OS} + V_N$ )· $m_2(t)$  est :

$$S_{CS}(f) = \sum_{k=-\infty}^{\infty} |M_{2k+1}|^2 S_N\left(f - \frac{2k+1}{T}\right) = \left(\frac{2}{\pi}\right)^2 \sum_{k=-\infty}^{\infty} \frac{1}{(2k+1)^2} S_N\left(f - \frac{2k+1}{T}\right) (II.26)$$

Donc le bruit et le décalage DC sont convertis aux fréquences harmoniques impaires du signal de modulation, laissant l'amplificateur à découpage idéalement sans aucun bruit offset ou basse fréquence. Dans une situation moins idéale, l'amplificateur aurait une largeur de bande limitée, par exemple jusqu'à deux fois la fréquence de découpage avec un gain constant.

#### II. 12Conclusion

Au court de ce deuxième chapitre, nous avons donné une brève introduction du CMOS et leurs régimes de fonctionnement, ainsi que les caractéristiques.

Nous pouvons de même souligner que le transistor CMOS est intéressant compte tenu des performances électriques qu'il offre. La difficulté majeure dans son développement se situe au niveau technologique.

# Chapitre 3

Simulation et Résultats

## **III.1 Introduction**

Instruments médicaux de diagnostic peuvent être effectués dans des dispositifs portatifs aux fins de soins à domicile, tels que le diagnostic de maladie cardiaque. Ainsi, pour des raisons de la portabilité et la durabilité, les concepteurs devraient réduire la consommation d'énergie des appareils autant que possible de prolonger leur durée de vie de la batterie.

A l'aide de la technologie de circuit intégré, l'exigence d'économie d'énergie de l'équipement portatif et durable donne aux concepteurs de circuits intégrer l'impulsion pour réduire la consommation d'énergie des circuits analogiques comme l'amplificateur opérationnel dans les systèmes d'acquisition du signal ECG.

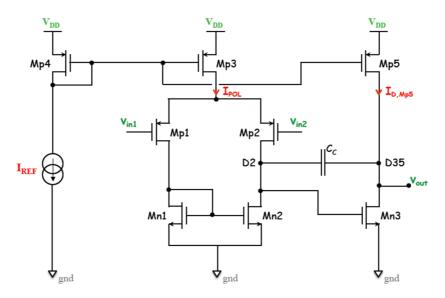

Ce chapitre présente l'analyse et les résultats de simulation de l'amplificateur opérationnel, ainsi que son implémentation dans la technologie 90nm CMOS. L'ensemble du système est consisté en deux étages essentiels, le premier c'est le circuit amplificateur différentielle et le deuxième c'est l'amplificateur source commun.

Le cahier de charge présente une haute performance à deux étages amplificateur opérationnel pour des applications médicales. Ces deux étages sont conçus pour un faible bruit, faible puissance, grand PSRR et très grand CMRR. La technique de compensation Miller (Cc) est utilisée un nulling active résistance (Rz) en utilisant des transistors de transmission Gate pour un fonctionnement stable en mode de réaction. L'amplificateur opérationnel a été fabriqué dans un SPECTRE utilisant GPDK technologie CMOS 90nm avec des tensions de seuil de 0.17 V et –0.14 V à 1V. Afin de mieux caractériser la réalisation d'un amplificateur opérationnel, l'étude qui suit s'attache tout d'abord à déterminer les caractéristiques du miroir de courant de base, qui sont l'élément essentiel d'un AOP puis à détailler la conception en technologie CMOS 90nm.

#### III.2 Miroirs de courant et leurs limitations

Cette partie est consacrée à la conception et à la simulation de deux types de miroirs de courant, miroir de courant simple et miroir de courant cascode.

## III.2.1. Miroir de courant simple

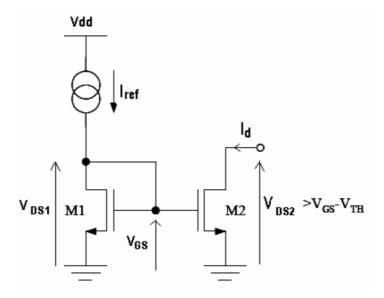

La figure III.1 présente un miroir de courant simple.

Fig.III.1. Miroir de courant simple

## Test du miroir de courant simple

Avant toute simulation, le concepteur doit établir un circuit de Test prenant en considération les entées et les sorties du bloque à simuler.

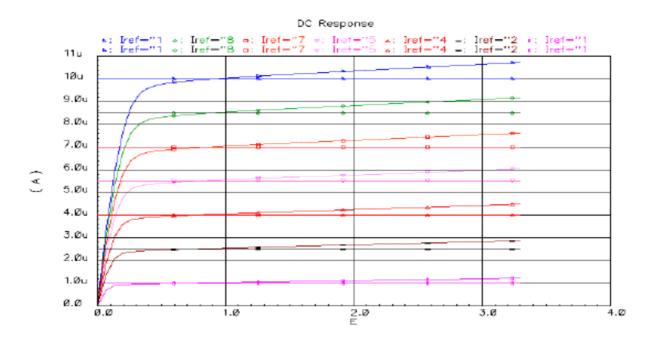

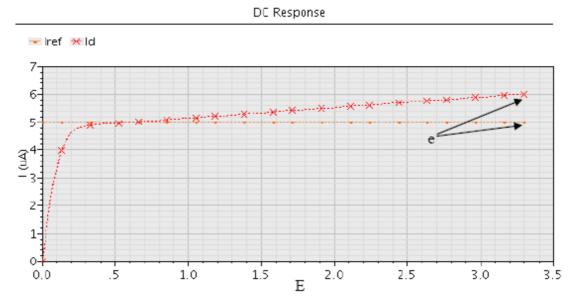

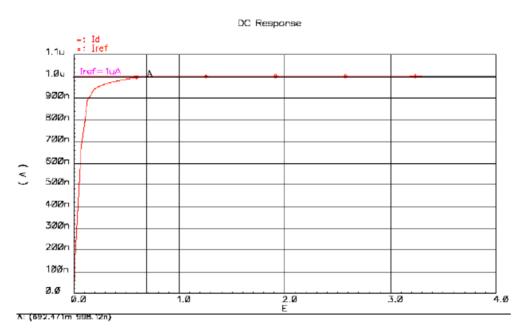

Le but de cette simulation est de connaître la variation du courant  $I_d$ en fonction de la tension d'entrée E. La variation de  $I_d$ est comparée au courant de référence $I_{REF}$ .

Pour les différentes valeurs du courant de référence  $I_{REF}$  , on obtient les résultats de la simulation présentés dans la figure III.2

Fig. III.2. Résultats de la simulation

La figure III.3 montre la variation du courant Id en fonction de la tension d'entrée E avec les dimensions des deux transistors: W (M1)=W (M2)=1um, et L (M1)=L (M2)=1um.

Fig. III.3. Résultats de la simulation

Les résultats de la simulation nous indique que :

$$e = I_d - I_{ref} = 0.222uA$$

$$V_{DSsat} = 584.33 mV$$

Où

(e): est l'erreur du miroir de courant simple.

V<sub>DSsat</sub>: La tension de saturation du transistor M2

Afin de minimiser l'erreur (e) une optimisation du miroir de courant est nécessaire

#### Optimisation du miroir de courant

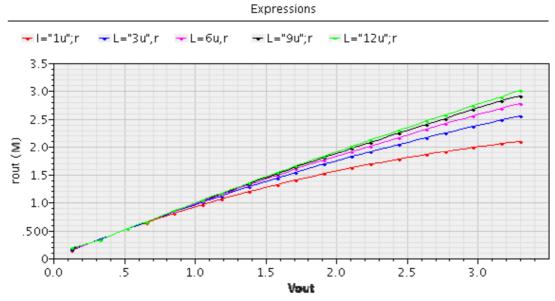

L'optimisation du miroir de courant nous mène à bien déterminer les deux dimensions w et L du transistor. En tenant compte de la résistance de sortie  $R_{ds}$ , la figure III.4 représente la variation de  $R_{ds}$  selon la tension E à plusieurs valeurs de L.

En fixant W (premier cas W=2um, deuxième cas W=4um) et augmentant L pour minimiser l'erreur du miroir de courant simple, on obtient le tableau III.1contenant les résultats de l'erreur du miroir de courant simple.

Fig. III.4. Résultats de la simulation

Si on augmente W pour les mêmes valeurs de L, l'erreur (e) augmente également. La figure III.5 présente les courbes du miroir de courant, et on peut bien constater que l'erreur (e) diminue à l'augmentation de L.

Fig. III.5. Résultats de la simulation

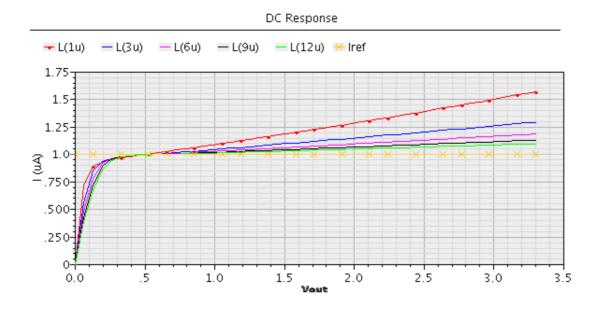

#### III.2.b Miroir de courant cascode

Figure III.6 indique le schéma du miroir de courant cascode avec quatre transistorsM1, M2, M3 et M4.

Test du miroir de courant cascode

Cette simulation présente la variation du courant  $I_d$  en fonction de la tension d'entrée E. La variation de  $I_d$  est comparée au courant de référence Iref . La figure III.6 montre le circuit Test du miroir de courant cascode.

Fig. III.6. Résultats de la simulation

La figure III.7 présente les résultats de la simulation pour un seul courant Iref selon les paramètres géométriques (W/L=1) de tous les transistors du miroir de courant cascode.

#### On obtient:

- L'erreur (e) est nulle.

- V DSsat = 692.47mV La tension de saturation de deux transistors M2 et M4.

Dans toutes les simulations précédentes des deux miroirs de courant simple et cascode,

## on peut conclure que:

- Si on augmente L, l'erreur du miroir de courant simple se minimise mais ne s'annule pas

- L'augmentation des deux paramètres W et L implique l'augmentation de la dimension

des transistors, ce qui provoque l'agrandissement du chip.

Fig. III.7. Résultats de la simulation

La tension minimale pour le miroir de courant simple le (V mV DS sat = 584.221) est mieux que la tension minimale pour le miroir de courant cascode (V mV DS sat = 692.47)

## II.3 Amplificateur opérationnel à deux étages

La figure III.8 montre Le schéma bloque de notre système c'est le signal ECG et AOP

Fig.III.8 le schéma bloque de notre système

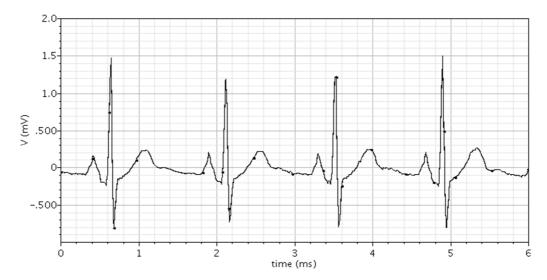

## III.3.a Signal ECG

Le signal ECG qu'est acquis dans la plage de 8uV à 5mV. En raison du faible niveau de tension, le signal est introduit dans un circuit d'amplification pour amplifier à un niveau de tension souhaitable. Pour la création de la base de données de battements cardiaques connus nous utiliserons les enregistrements de la base de données du MIT/BIH arrhythmia. Nous avons collecté ces base de données MIT/BIH arrhythmia, pour entraînement et tests de projet de conception d'amplificateur opérationnel du signal ECG. La figure III.9 montre un exemple

d'un tracé ECG normal par Matlab avec d'entée ( $V_{IN}$ ) en fonction de temps, qui est constitué d'une onde P, complexe QRS et onde T.

**Fig.III.9** Représentation d'un signal ECG normal par matlab de la base de données **MIT-BIH Arrhythmia.**

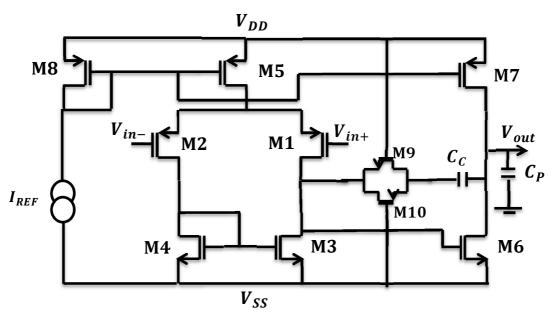

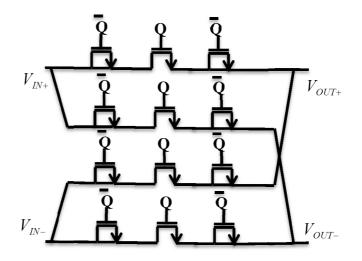

## III.3.b Amplificateur Opérationnel

La structure générale de l'amplificateur opérationnel à deux étages en technologie CMOS 90nm avec circuit de compensation est représentée sur la Figure III.10.

Le premier étage dans la Figure. III.10 est constitué par une paire différentielle à canal P (M1-M2) avec un miroir de courant à canal N (M3-M4) et d'un transistor (M5) de source de courant d'extrémité à canal P.

Le deuxième étage consiste un amplificateur à source commune à canal N transistor (M6) avec une source de courant de charge à canal P transistor (M7). Les résistances de sortie élevée de ces deux transistors (M6, M7) assimilent relativement grand gain pour cet étage et un gain modéré pour l'amplificateur complet. Du fait que les entrées d'amplificateurs opérationnels sont connectées aux grilles des transistors MOS, la résistance d'entrée est essentiellement infinie. Les tailles des transistors ont été conçue pour un courant de référence de 1uA

Fig.III.10 schéma de l'amplificateur opérationnel à deux étages

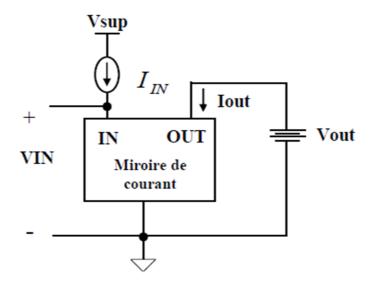

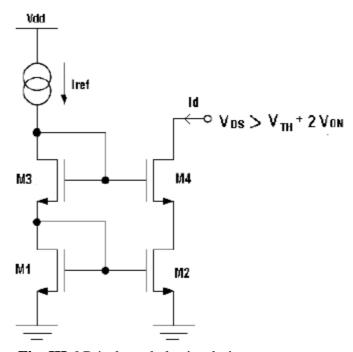

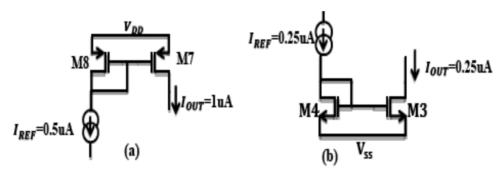

#### III.3.b.1 Miroir de courant

Des miroirs de courant sont largement utilisés dans les circuits analogiques MOS, les deux éléments de polarisation et active charge pour obtenir un Gain élevée en tension AC. Des transistors à mode d'enrichissement restent en saturation lorsque la grille est liée au drain, en tant que la tension drain-source  $(V_{DS})$  est supérieure à la tension grille-source  $(V_{GS})$  dû de la tension de seuil  $(V_{TH})$  baisse :

$$V_{DS} > V_{GS} - V_{TH}({\rm III.1})$$

Selon Eq (5.1), les sources de courant constant sont obtenues par des miroirs de courant destinés à faire passer un courant de référence à travers un transistor à diode connecté (grille lié au drain). Nous choisissons un simple miroir de courant car basse tension (1-V), Figure IV.5 (a) et (b) montrent la conception de miroir de courant PMOS et NMOS. Un miroir PMOS servir comme source de courant tandis que le NMOS agit comme un collecteur de courant.

La tension développée aux bornes du transistor connecté en diode est appliqué à la grille et la source du deuxième transistor, qui fournit un courant de sortie constant. Comme les deux transistors ont la même tension grille-source, les courants lorsque les deux transistors sont dans la zone de saturation de fonctionnement, sont régies par Eq (III.2) et Eq (III.3), en

supposant transistors appariés. Le rapport de courant  $I_{OUT}/I_{REF}$  est déterminé par les rapports d'aspect du transistor.

Le courant de référence qui a été utilisé dans la conception est 0.5µA. Le courant de sortie est désiré 1uA.

Pour le miroir de courant PMOS, nous pouvons écrire,

$$\frac{I_{OUT}}{I_{REF}} = \frac{\frac{W_7}{L_7}}{\frac{W_8}{L_8}} (III.2)$$

Pour le miroir de courant NMOS, nous pouvons écrire,

$$\frac{I_{OUT}}{I_{REF}} = \frac{\frac{W_4}{L_4}}{\frac{W_3}{L_3}} (III.3)$$

Fig.III.11Miroir de courant type NMOS et PMOS

#### III.3.b.2. Résistance Active

Il existe deux types de résistance active utilisée dans la conception. La première, le courant de référence qui est appliqué à miroir de courant est obtenu par l'intermédiaire d'une résistance active. La résistance est obtenue en reliant simplement la grille d'un MOS à canal N (M11) à son drain comme représenté sur la Figure.III.12. Cette connexion force le transistor MOS fonctionné dans la région de saturation.

La deuxième résistance active c'est une porte de transmission (Transmission Gate) représentée sur la Figure.III.13, elle a été utilisée pour réaliser la résistance de contreréaction d'annulation active (R\_Z) pour réduire les effets du zéro plan de droite dans la fonction de

transfert. La grille de ces transistors M9, M10 est polarisée à VDD, VSS respectivement. Son faible résistance de sortie est obtenue à partir Eq (III.4) et Eq (III.5) (Vds très petit).

Fig.III.12. Résistance active

Les limites de la plage dynamique associée à un seul canal commutateurs MOS peuvent être évitées avec interrupteur CMOS. L'utilisation de la technologie CMOS, un commutateur généralement construits en connectant le transistor à canal P en parallèle avec le transistor à canal N comme illustré.

Fig.III.13Porte de la transmission

Pour cette configuration, lorsque Q est à l'état bas; les deux transistors sont bloqués, le circuit est ouvert. Lorsque Q est à l'état haut, les deux transistors sont active, donner un état de faible impédance. La tension de bulk des transistors NMOS et PMOS sont prises aux potentiels les plus élevés et les plus bas, respectivement. Le principal avantage des CMOS basculer sur le canal seul commutateur MOS est que la plage analogique-dynamique unique dans l'état ON est fortement augmentée

$$R_{ON} = \frac{1}{U_N C_{OX} \frac{W}{L} (V_{GS} - V_{THn})}$$

(III.4)

$$R_{ON} = \frac{1}{U_P C_{OX} \frac{W}{L} (V_{SG} - |V_{THp}|)}$$

(III.5)

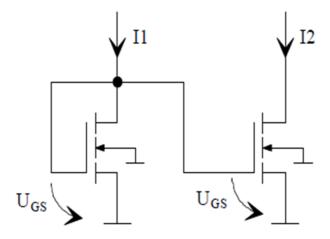

## III.4.Structure de chopper stabilisé

Pour les commutateurs de modulation et de démodulation, la structure de commutateur différentiel MOS à canal N qui est représenté sur la figure.III.14 Le circuit de modulateur, qui est placé avant l'amplificateur opérationnel chopper stabilisé, est essentiel à la gamme des non-linéarités et le bruit. Par conséquent, pour faible bruit à deux étages d'amplificateur opérationnel, une attention critique doit être accordée à la conception de la partie de modulateur pour minimiser mieux le bruit et la tension de décalage

Fig.III.14 Différentielle commentateur de type NMOS

Clock-feedthrough et l'injection de charge sont les principaux facteurs entraînant la nonlinéarité dans les commutateurs MOS. La Figure.III.15 montre chopper circuit différentielle de type NMOS avec la moitié de commutateur dummy.

**Fig.III.15.**Différentielle commentateur de type NMOS avec Dummy

## **III.5. Simulation et Discussion**

L'amplificateur opérationnel à deux étages proposé est constitué d'un amplificateur différentiel et un chopper stabilisé. Les sous-sections suivantes décrivent la simulation de chaque module.

## III.5.a. Paramètre de dispositif

Le tableau 1 donne le paramètre de dispositif pour un amplificateur opérationnel à deux étages.

| Dispositif | Type | W(um) | L(um) |

|------------|------|-------|-------|

| M1,M2      | P    | 10    | 0.378 |

| M3,M4      | N    | 18    | 0.556 |

| M5,M8      | P    | 35    | 0.460 |

| M7         | P    | 80    | 0.530 |

| M6         | N    | 15    | 0.100 |

| M9         | N    | 1     | 0.100 |

| M10        | P    | 10    | 0.100 |

| M11        | N    | 3     | 0.800 |

**Tab 1** Paramètre de l'amplificateur opérationnel

## III.5.b. Réponse en fréquence, Compensation